RFID

Записал коды с 3-х брелков логическим анализатором Ulogic (нету цифрового осцилла ![]() - пришлось изгаляться с LPT портом). На второй вход подавал синро F/64 с доп. выхода МК. Приёмник самодельный, за отсутствием в продаже спецмикрух.

- пришлось изгаляться с LPT портом). На второй вход подавал синро F/64 с доп. выхода МК. Приёмник самодельный, за отсутствием в продаже спецмикрух.

Выяснил: манчестер, F/64 на бит, всего 64 бита, АМ. В начале идут 9 единиц. Похожи и на EM4100, EM4102.

тогда дело в шляпе, заполнение буфера на 64 бита реализовано в прерывании, алгоритм поиска заголовка и подсчета контрольной суммы присутствует в исходнике,указанном мной выше. структура пакета описана в доке на EM4100.

Почитал немного ДШ. ![]() и возникло 2 вопроса (после праздников думается туго):

и возникло 2 вопроса (после праздников думается туго):

1. Как записывать последовательность в буфер, не имея clock, ведь последовательное к-во подряд нулей и единиц выглядит одинаково?

2. Стоит ли заморачиваться с подсчётами бит чётности по строкам и столбцам? Может найти в буфере заголовок (9 единиц) и, зная начало, считать всё кодом ключа? Проще сравнивать с EEPROM. Большое к-во ключей хранить не нужно.

DDR, может алгоритмы нарисуете от руки в виде логических блоков, а то расшифровывать asm для pic мне тяжело. Можно на мыло (в профиле) в любом виде.

smg123

Можно фото вашего ключа.

Фото здесь.

Разбирался с документацией и исходником от DDR. Голова уже кругом. Решение где-то рядом, но не даётся. Отложил до завтра-послезавтра.

процесс считывания метки можно условно разделить на два этапа:

1. это синхронизация потока передачи метки с буфером приемника ридера - вовсе не обязательно ждать девяти импульсов заголовка, код манчестера самосинхронизирующийся и состоит из фронтов подготовки уровня сигнала и фронта спада либо подьема - сигнализирующего о том единицу либо ноль передать. Задачча синхронизации - четко определить текущее изменение уровня - информационное или подготовка. Алгоритм вхождения в синхронизацию следующий - ждем первое изменение уровня, ждем второе - если между этими изменениями уровней удлинненный по времени импульс, то второе изменение уровня - это информационный сигнал, т.е после прихода удлиненного импульса начинаем считывание в буфер 64 бит данных(и не важно какую строку или бит в данный момент передает ключ, он всеравно циклично крутит по кругу свой пакет ).

2. Обработка буфера принятых данных - крутим по кольцу 64 битный буфер до тех пор пока не обнаружим 9 идущих подряд бит заголовка (если прокрутили буфер по кругу и не обнаружили - сответственно принимаем решение о том что в буфере мусор)

3. После обнаружения заголовка по известной структуре пакета передачи транспондера вычисляем биты четности по строкам и по столбцам и сравниваем их с переданной контрольной суммой.

в приложении есть исходник на Си, может будет попроще разобраться

PS используемые мною метки один в один похожи на выложенные на фото это 100% EM Marine

smg123: Записал коды с 3-х брелков логическим анализатором Ulogic (нету цифрового осцилла - пришлось изгаляться с LPT портом

Уххх, круто, я протупил, и для этих целей купил USB осциллограф, вещь не дорогая и идеально подошла для анализа пакета посылки транспондера

вот тут выдержка из форума по декодированию манчестера

Мне проще эмулятор ключа сделать, чем декодировать манчестер. ![]()

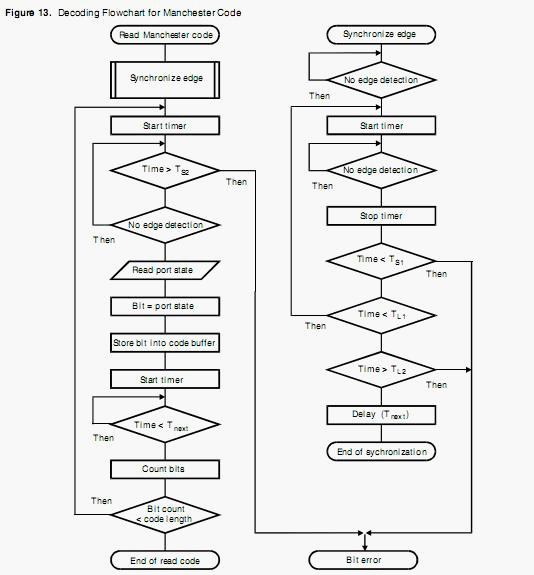

Поиски увенчались успехом. Нашёл алгоритм декодера у Atmel. Для моего такта в 512 мкс их рекомендации придётся удвоить: TS1=180, TS2=360, TL1=420, TL2=600 мкс. Tnext=TS2. Должен заработать.

у меня TS1=128мкс TS2=384мкс=TL1 TL2=640мкс