Что-то нифига у меня не работает счетный триггер на 4х элементах И-НЕ

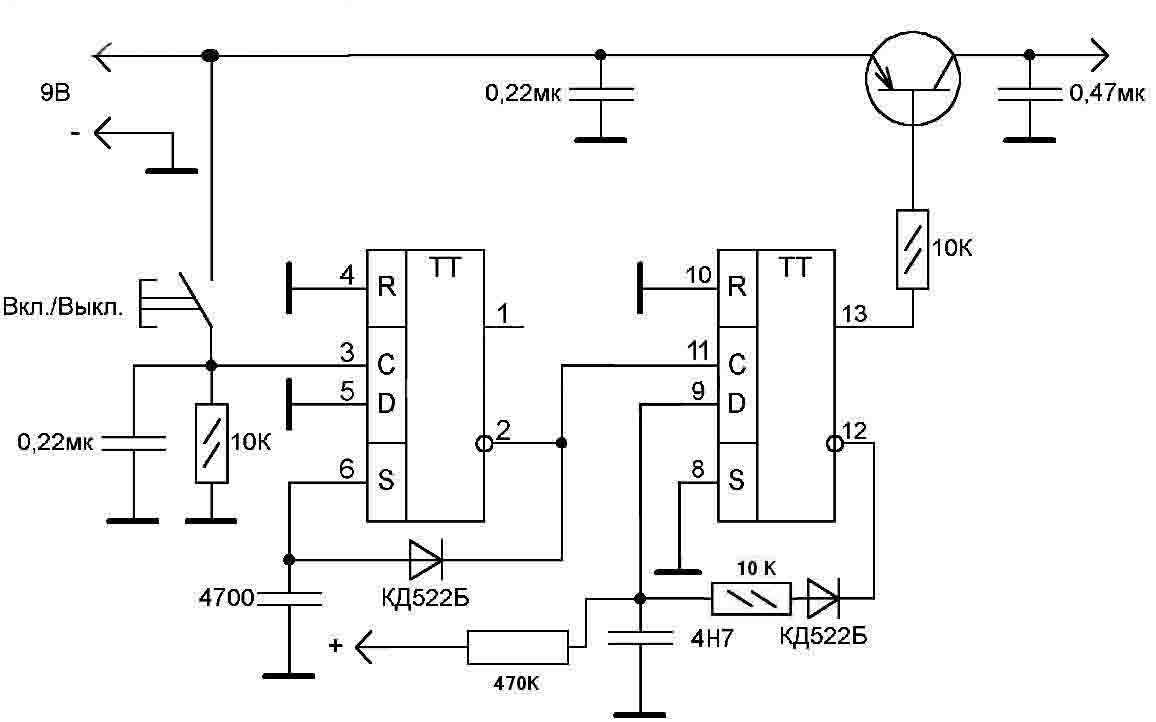

Nintashi: Если имеем CD4013B, то тогда можно применить схему, которую предложил DVD несколькими постами выше (вторая страница, схема с обычной кнопкой), чуть изменив схему включения второго D-триггера, дабы исключить самостоятельное выключение устройства по истечении нескольких минут и сделать работу устройства более устойчивой... т.е. 8 вывод посадить на массу, конденсатор с диодом засадить на 9 вывод (предварительно убрав соединение между 9 и 12 выводами, заодно уменьшив емкость конденсатора хотя бы до тех же 4,7 наны). Чтобы гонка сигналов внутри триггера была еще менее обострена последовательно с диодом поставить резистор килоом на 10, а точку соединения конденсатора и вывода 9 подтянуть к питанию через килоом 470. Цепь замедлит смену сигнала на 9 выводе, а значит триггер будет работать гарантировано устойчиво.

Сложно понятно. Главный вопрос - зачем вообще применять обе половины микросхемы.

Может быть применение Филипса с гистерезисом здесь более чем оправданно и стоит поискать его? Можеть быть, оправданно зашунтировать питание триггера емкостью? Может быть, на Vdd сопротивление поставить перед емкостью? Потребление микросхемы мизерное - можно и килоом бабахнуть?

Общетеоретический к вам вопрос: некая микросхема, в ней некий логический элемент (компаратор, ОУ и т.п.) находится в пресловутом аналоговом режиме, т.е. на вход/входы подано напряжение, точно соответствующее граничному. Милливольт туда-сюда и выход заваливается в максимум-минимум. При уменьшении/повышении напряжения питания микросхемы - потенциал критической точки уменьшится/увеличится? Или нельзя так просто сказать?

ZZZAMK: обе половины микросхемы

Первая формирует четкий импульс по фронту... т.е. уже становиться неважно, сколько будет нажата кнопка, вторая половина - сам счетный триггер. Приду с работы, нарисую и вложу, как я себе это все представляю. Заодно, попытаюсь объяснить почему вставлена та или иная деталь.

ZZZAMK: Зачем вообще два (2) триггера, не пойму?

В принципе - для универсальности. Что бы можно было использовать узел в разных приложениях, не зависимо от типа управления (одно, двух-полюсные кнопки с замыканием-размыканием на корпус, на питание или на какой-то уровень напряжения, сенсорный или иной датчик) и не зависимо от исполнительного устройства (транзистор той или иной проводимости, реле, тиристор и т.д.).

Первый триггер устраняет дребезг, а второй - переключает выход в одно из устойчивых состояний.

Можно по схеме, прведенной 6П3С: А я применяю схему на одном D триггере... ( http://pro-radio.ru/start/8872-2/2009/12/05/14-03-22/ )

Ещё один более универсальный вариант - в аттаче. Просто, как пример.

Схема не собиралась, а указанные номера телефонов уже не действительны...

Коммутация четырёх линий на один телефон с удержанием и конференцией.

Вместо D-триггеров использован регистр. На триггерах потребовалось бы в 2 раза больше корпусов.

Верхний по схеме регистр управляется кратковременным нажатием, а нижний - длинным. То есть, при кратковременном нажатии на одну из кнопок, сработает только один из выходов верхнего регистра (к телефону подключится одна из линий). А если кнопку нажать и удерживать более 2 секунд, то сработает один из выводов и нижнего регистра (выбранная линия включится на удержание и после этого можно переключиться на другой номер, кратковременно нажав другую кнопку).

Дребезг устраняется тем, что состояние кнопки записывается в регистр только через определённое время (~50мсек для верхнего регистра и ~2сек для нижнего). То есть, состояние кнопки записывается только когда оно "устаканится".

Вроде дорисовал

Теперь о доработке. Естественно, что я убрал из схемы переворачивание второго триггера в выключенное состояние (для этого отключил подачу сигнала с инверсного выхода на вход SET. Далее введя резистор последовательно с диодом замедлил смену уровня сигнала на входе D второго триггера, тем самым исключив гонку сигналов внутри самого триггера. Вход D подтянут к питанию потому как диод все же может иметь утечку.

Nintashi, я не пойму, что Вы получили изменением схемы по сравнению с исходным вариантом?

Я приводил этот вариант с автовыключением, так как он использовался для включения-выключения мультиметра, и схема принудительно выключала его питание через несколько минут, если забыть его выключить.

Если автовыключение не требуется, то нужно, всего лишь, соединить оставить соединённые между собой вход "D" и инверсный выход второго триггера, убрав диод с конденсатором. Всё. После этого второй триггер будет просто переключаться из одного состояния в другое при каждом нажатии на кнопку и оставаться в этом состоянии до последующего нажатия.

Зачем наворачивать кучку деталей второму триггеру в вашем варианте? Что они дают? Что улучшают?

P.S.

По сравнению с простым замыканием D-входа с инверсным выходом, ваша схема выполняет те же функции. Так зачем ставить лишние детали?.. ![]()

Я было сначала тоже так подумал, но зная, что чипы друг от друга отличаются я подумал, что лучше будет не ставить триггер в положение когда при условно "медленном" фронте на входе "С" триггер переключается и на входе D, данные с которого попросту транслируются на выход по приходу импульса синхронизации, при этом сменится логическое значение. Ситуация может случиться такая, как в самом начале этой темы. Так что эти детальки поставлены чисто из-за перестраховки.

ZZZAMK: Или нельзя так просто сказать?

Так... во первых все таки аналоговый или цифровой элемент. Ответы будут несколько различны. А для цифрового элемента именно так - сказать ничего нельзя. Использование цифрового элемента в аналоговом режиме - нештатное использование и как он при этом себя ведет - зависит от конкретного экземпляра микросхемы. В этом случае можно говорить лишь об общей тенденции.

Nintashi: Так что эти детальки поставлены чисто из-за перестраховки.

Как в "Ералаш"-е:

- Мальчик, ты зачем себе два билета компостируешь?

- А вдруг один потеряю, другой хоть останется!

- А если ты и второй билет потеряешь?

- А у меня на этот случай проездной есть...![]()

Даже с мс простой логики (ЛА7, ЛЕ5 и др.), в элементах которой выход сильно связан со входом (последовательное включение двух-трёх каскадов с большим коэффициентом усиления) возможна работа в компараторном режиме, когда медленное изменение напряжения на одном из входов, сравнявшись с постоянным напряжением на втором, резко переключает выход в другое состояние. Я добивался уверенной отработки разницы в десятки мВ.

Эти элементы использовались как ШИ-модуляторы на чатотах до сотен КГц даже в промышленных устройствах (например, преобразователь в БП радиоудлинителя "Алтай").

То есть, довольно быстро переходят из одного состояния в другое.

Единственный недосток такого режима - повышенный потребляемый ток (до 10мА) в близи порога (входное напряжение вблизи половины напряжения питания).

Единственным условием, заставляющим выход этих элементов повторять входное напряжение, является введение ООС.

У более развитой логики, с большим числом элементарных усилительных каскадов и с перекрёстными связями между ними, медленное изменение выхода почти невозможно.

По этому, даже относительно медленное нарастание тактового импульса, заставляет триггер уверенно переключаться.

Для обсуждаемой схемы - главное, что бы переключающий импульс на второй триггер приходил "в одиночку", а не "толпой", потому что каждый перепад переключает триггер в противоположное состояние, в то время как требуется это делать однократно - одно нажатие соответствует одному переключению.

По этому и стоит первый триггер, выполняющий роль подавителя дребезга - любой первый же перепад напряжения на его тактовом входе перебросит этот триггер в одно устойчивое состояние, заставит его выдать ровно один быстрый перепад на второй ториггер и после этого перестать воспринимать любые импульсы на входе в течение времени, определяемом постоянной времени цепи сброса (сопротивление обратносмещённого диода с выхода на вход сброса первого триггера и конденсатор).

При постоянной времени этой цепи более 50мсек, дребезг уверенно подавляется, а если же увеличить постоянную до, например, 1сек, то повторное переключение станет возможным не ранее, чем через 1сек. Даже при подаче на вход меандра с любой частотой, не говоря уже о каком-то дребезге...